innolinkchiplet互联标准解决方案

3月份 , Intel、台积电、三星、日月光、AMD、ARM、高通、Google、微软、Meta(Facebook)等行业巨头联合 , 推出了全新的通用芯片互联标准——UCle 。

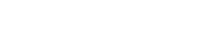

几乎同一时间 , 中国芯片厂商芯动科技(Innosilicon)宣布 , 率先推出国产自主研发的物理层兼容UCIe国际标准的IP解决方案“InnolinkChiplet” , 是国内首套跨工艺、跨封装的Chiplet连接解决方案 。

根据芯动科技官方最新消息 , 该方案已经在先进工艺上量产验证成功!

文章图片

文章图片

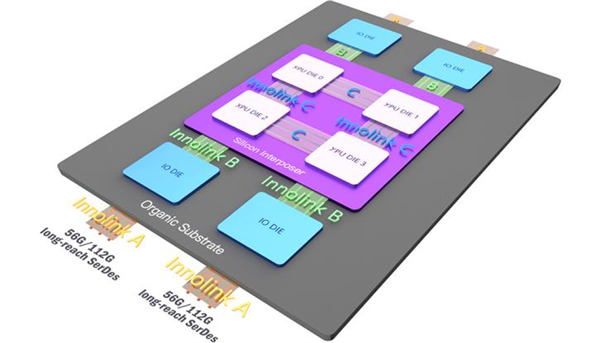

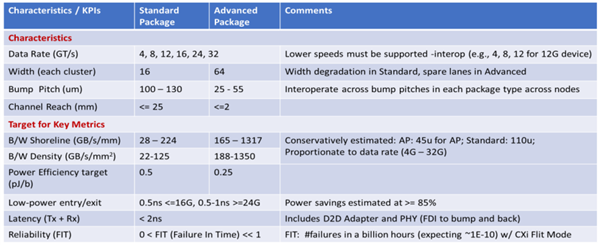

Chiplet(小芯片/芯粒)技术的核心是多芯粒(Die-to-Die)互联 , 利用更短距离、更低功耗、更高密度的芯片裸Die间连接方式 , 突破单晶片(monolithic)的性能和良率瓶颈 , 降低大规模芯片的开发时间、成本、风险 , 实现异构复杂高性能SoC的集成 , 满足不同厂商的芯粒之间的互联需求 , 达到产品的最佳性能和长生命周期 。

Intel、AMD、NVIDIA、苹果等新品巨头都有了此类产品 , 台积电等代工厂商也在推进相关工艺技术 , 但实现路径、技术标准各不相同 。

UCIe标准就是把它们统一起来 , 实现不同IP芯粒之间的高速互联 , 将芯片设计公司、EDA设计厂商、代工厂商、封测厂商等上下游产业链联合在一起 。

文章图片

文章图片

芯动科技称 , 自己在Chiplet技术领域积累了大量的客户应用需求经验 , 并且和台积电、Intel、三星、美光等业界领军企业有密切的技术沟通和合作探索 , 两年前就开始了Innolink的研发工作 , 率先明确InnolinkB/C基于DDR的技术路线 , 2020年首次向业界公开InnolinkA/B/C技术 。

Innolink的物理层与UCIe的标准保持一致 , 成为国内首发、世界领先的自主UCIeChiplet解决方案 。

文章图片

文章图片

文章图片

文章图片

InnolinkChiplet的设计思路和技术特点:

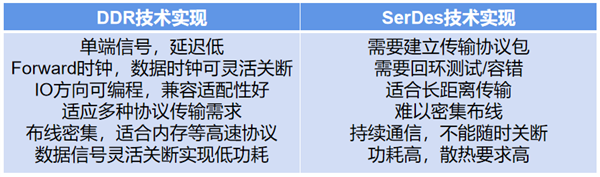

1、业界很多公司认为 , Chiplet跨工艺、跨封装的特性 , 会使其面临复杂的信号衰减路径 , 所以普遍使用SerDes差分技术以应对这一问题 。

芯动科技则认为 , 相较于SerDes路线 , DDR技术更适合Chiplet互联和典型应用 , 而且不同封装场景需要用到不同的DDR技术方案 , 为此提供基于GDDR6/LPDDR5技术的高速、高密度、高带宽连接方案 。

2、Chiplet互连在短距PCB、基板、中介层上连接时 , 路径短、干扰少、信号完整性好 , 采用DDR技术路线在延时功耗、带宽密度上更具优势 。

文章图片

文章图片

3、标准封装使用MCM传统基板作为Chiplet互联的介质 , 成本低特点 , 是对成本较为敏感的Chiplet应用场景首选;Interposer中介层等先进封装具备密度高、良品率低、成本高等特点 , 是对价格不敏感的高性能应用场景首选 。

UCIe定义正式发布前 , Innolink-B/C就提前实现了这两种封装场景的应用 , 验证了对市场前景和Chiplet技术趋势的准确判断 。

文章图片

文章图片

4、针对长距离PCB、线缆的Chiplet连接 , Innolink-A提供基于SerDes差分信号的连接方案 , 以补偿长路径的信号衰减 。

- 车企造手机?天真!

- 企业现场签约!青岛市工业互联网复工复产“场景周”即墨区专场活动举行

- 工信部:支持高校设置工业互联网相关二级学科或交叉学科

- 智慧党建管理平台,标准化数字党建阵地,助力党组织打造特色党建

- 青岛高新区:以工业互联网平台赋能“高新”制造

- 电子烟强制性国家标准10月起实施 解读:5%尼古丁烟弹将告别市场

- 联想官宣国产生态DISC,以ZUI和设备互联为内核

- 农业元宇宙大咖谈 | 王冠雄:虚拟人或是农业互联网经济“新入口”

- 电池寿命是行业标准的2倍!一加Ace入网

- 一加Ace曝光:首次搭载长寿版150W 电池寿命是行业标准的