三星新型3nmgaa晶体管的性能提高了23%

文章图片

文章图片

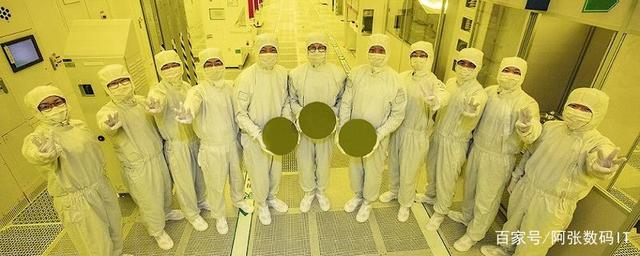

三星声称其新型3nmGAA晶体管的性能提高了23%

在硅市场中 , 相对较少的制造商自己生产芯片 , 大多数公司设计自己的产品 , 并聘请专门的硅代工厂为他们生产芯片 。这降低了研发成本 , 并确保获得最新的硅制造技术 。

领先的硅晶圆代工市场由三星和台积电两大主要参与者主导 , 这两家公司都在不断争夺成为半导体市场的领先制造商 。近年来 , 台积电一直领先于三星 , 但随着3nm光刻节点的推出 , 这种情况可能很快就会改变 。

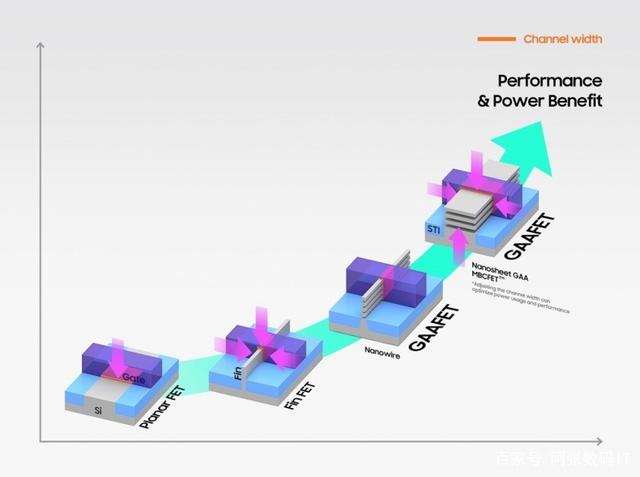

三星已经开始使用其3nmGate-All-Round(GAA)晶体管架构生产硅 。GAA晶体管是一种后鳍式场效应晶体管设计 , 可提供改进的性能特征 。三星版本的GAA晶体管称为多桥通道FET(MBCFET) , 它改进了标准的GAA概念 , 具有更宽的通道宽度和纳米片 。

GAA(Gate-All-Round)它克服了FinFET晶体管的尺寸和性能限制 , 在通道的各个侧面都有四个栅极 , 以提供全面覆盖 。相比之下 , FinFET有效地覆盖了鳍状(因此FinFET)通道的三个侧面 。实际上 , GAAFET将三维晶体管的想法提升到了一个新的水平 。

凭借其第一代3nmMBCFET晶体管 , 三星声称其5nm节点可提供高达45%的效率增益 , 高达23%的性能提升 , 以及高达16%的面积减少 。凭借其第二代3nm工艺 , 三星计划与5nm相比 , 功耗降低多达50% , 性能提升高达30% , 面积减少35% 。

凭借其最新的光刻节点 , 三星可以让制造商创建更节能、更高性能、更密集的晶体管芯片 。如果这些说法属实 , 三星应该能够在台积电面前大获全胜 , 并可能在此过程中赢得一些知名客户 。

以下是三星关于其新型3nmGAA晶体管的图片 , 这些晶体管现在正用于在三星的代工厂生产芯片 。

文章图片

文章图片

设计技术优化 , 实现性能功耗价值最大化

三星的专有技术利用具有更宽通道的纳米片 , 与使用具有更窄通道的纳米线的GAA技术相比 , 可实现更高的性能和更高的能源效率 。利用3nmGAA技术 , 三星将能够调整纳米片的通道宽度 , 以优化功耗和性能 , 以满足各种客户需求 。此外 , GAA的设计灵活性对设计技术协同优化(DTCO)非常有利 , 有助于提高功耗、性能、面积(PPA)的优势 。与5nm工艺相比 , 第一代3nm工艺可降低高达45%的功耗 , 与5nm相比 , 性能提高23% , 面积减少16% , 而第二代3nm工艺则可降低功耗高达50% , 性能提高30% , 面积减少35% 。

与SAFE合作伙伴一起提供3nm设计基础设施和服务

【三星新型3nmgaa晶体管的性能提高了23%】随着技术节点变得越来越小 , 芯片性能需求也越来越大 , IC设计人员面临着处理大量数据以验证具有更多功能和更紧密扩展的复杂产品的挑战 。为了满足这些需求 , 三星努力提供更稳定的设计环境 , 以帮助减少设计、验证和签核过程所需的时间 , 同时提高产品可靠性 。自2021年第三季度以来 , 三星电子通过与三星高级代工生态系统(SAFE)合作伙伴(包括Ansys , Cadence , Siemens和Synopsys)的广泛准备 , 提供经过验证的设计基础设施 , 以帮助客户在更短的时间内完善其产品 。

- 三星宣布推出isocell传感器

- 长征火箭创103次新连胜纪录 中国新型火箭研制进展如何?

- 三星galaxyzfold4价格曝光:1799欧元

- 手机需求下滑,三星在越南工厂减产

- ps5扩容为何选择三星980pro散热片版

- 连夺全省第一!济南在全国新型信息消费示范项目以及全省优秀数字产品中表现亮眼

- 三星galaxyzflip4公布详细参数

- 走在前 开新局|“十大创新”看淄博:高质量推进创新型城市建设

- 三星zfold4galaxyzfold4曝光

- 联想陈劲晒三星hp1主摄:大小比肩1元硬币