2nm以下的芯片导线选择( 二 )

掺杂能以几种方式进行 , 例如金属诱发技术利用石墨烯和铜、钌等金属的直接接触来产生结晶 。这些混合了金属和石墨烯的掺杂方法可以整合两种材料各自的最大优势:金属的高载子密度与石墨烯的高迁移率 。

本文探讨在2纳米以下的芯片导线中采用金属/石墨烯混合结构的可行性 。目前有两种结构正在进行研究 , 包括具备石墨烯覆盖层的金属组件 , 以及具备金属覆盖层的石墨烯组件 。本研究锁定钌金属 , 业界近期逐渐把它当作取代铜的金属布线材料 , 但这里提到的概念未来应该可以延伸到其他的导线金属材料上 。

采用钌覆盖层的石墨烯

本研究中 , IMEC团队将化学气相沉积(CVD)的多层石墨烯薄膜 , 转移到物理气相沉积(PVD)的钌金属薄膜(通常是5纳米)上面 , 最终制成混合了钌和石墨烯的组件结构 。结果发现 , 石墨烯在转移之后可以完整附着在大面积的钌金属薄膜上 。

在导线应用 , 石墨烯的金属诱发掺杂技术获得了市场关注 , 预计会让石墨烯在与钌接触的接口产生结晶 。为了了解并控制掺杂的结果 , 我们针对钌与石墨烯接触接口的电荷转移展开系统性研究 。

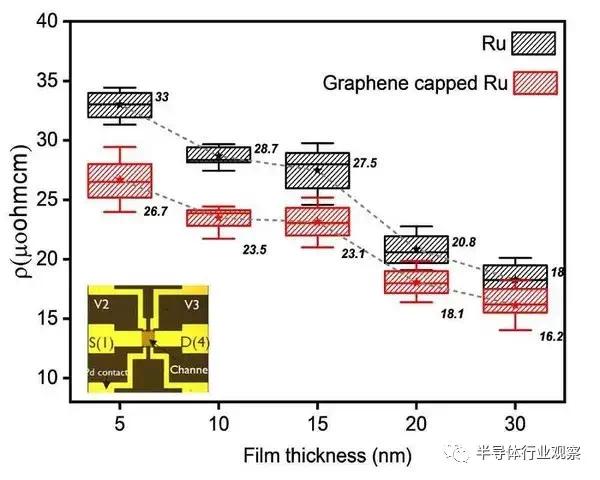

结果有两大发现:首先 , 研究人员发现钌在与石墨烯完成封装之后 , 薄膜电阻(sheet resistance)平均下降了15% 。第二 , 他们发现石墨烯的费米能阶下降 , 价带比纯石墨烯低了约0.5eV , 相当于1.9E13cm-2的电洞浓度 。这项发现指出 , 在界面发生的金属诱发掺杂现象 , 让石墨烯在作为钌金属的覆盖层时 , 会变成P型 。

文章图片

文章图片

图二 : 实验测量纯钌金属(黑色)与具备石墨烯覆盖层的钌组件(红色) , 在不同厚度的钌薄膜基板上的薄膜电阻值 。

经过本研究就可以确定钌在与石墨烯混合封装后 , 确实可以增加其作为导线的电气性能 。不过 , 覆盖层内的导电机制究竟如何运作 , 还需要更多基础研究来提供见解 。不论是将钌当作主要导体 , 辅以石墨烯来抑制金属内的散射机制 , 进而降低电阻 , 或是让这两种导体共同运作 , 其中 , 石墨烯会因为电荷迁移而具备比纯石墨烯还要高的导电性 , 这些混合方法现在都还在透过建立模型来取得更深入的了解 。

此外 , 值得注意的是 , 钌金属导线在与石墨烯封装后 , 对温度变化的敏感度也降低了 , 这可能源于石墨烯的高导热性 , 散热机制因为多了额外或替代的传导路径而变得更有效率 。这项发现也在开发未来的导线应用时引起关注 , 因为高度微缩的IC布线本身就会产生热能 , 其周围的介电组件散热能力又不足 , 导致芯片内部导线的热可靠度(thermal reliability)下降 。

整体而言研究人员下了个结论 , 那就是采用石墨烯覆盖层的混合金属结构提供了一套解决导线RC延迟的解决办法 。IMEC预期 , 这项技术未来能导入1纳米以下技术节点的后段制程 。

金属与石墨烯混合的夹层结构

长远来看 , IMEC团队为了进一步提升导电性 , 目前正在研究石墨烯与金属相互交替的堆栈结构 。以类似三明治的方式堆栈出金属/石墨烯/金属…的夹层结构时 , 就会有第二个、第三个…的不同接口 , 每个都发挥同等重要的作用 , 都是在石墨烯上方沉积金属层时的接触接口 。就像先前提到的研究结果 , 石墨烯和金属在接触接口自产产生的交互作用 , 能够改变石墨烯的物理特性 , 而且电子能带结构会因接口上的电荷分布而产生明显变化 。

不过 , 设计石墨烯和金属接口是一项巨大挑战 。通常(经过转移的)石墨烯层含有大量的非定向晶粒 , 这些晶界会充当线缺陷和上层表面金属沉积的晶粒成核中心位置 。运用PVD或原子层沉积(ALD)等传统方法时 , 要让金属均匀覆盖在整片石墨烯基面上会有困难 。而且石墨烯在转移后表面会受到杂质污染 , 所以需要采用合适的清洗方法 , 才不会损及石墨烯层 。

- 智库论坛 | 社区电商推动供应链数字化转型的对策建议

- 人类与AI如何共处?诺奖科学家、将棋天才、“低欲望社会”提出者的不同解答

- 线上新书发布!云上带你了解有关“冬奥”的那些事儿

- 我的世界大闹天宫龙宫怎么玩(我的世界大闹天宫龙宫打法技巧一览)

- 复苏的魔女竞技场用什么队伍(复苏的魔女竞技场队伍搭配心得分享)

- 复苏的魔女魔导装备boss怎么打(复苏的魔女魔导妨害装备获取攻略大全)

- 今年的iphonese,还是你熟悉的模样

- 长安福特蒙迪欧在中国市场的“全球化”

- safari浏览器中的indexeddb漏洞

- 复苏的魔女时空裂隙用什么阵容好(复苏的魔女时空裂隙阵容搭配指南)